Part Number: SN65MLVD204A

Tool/software:

Dear Technical Support Team,

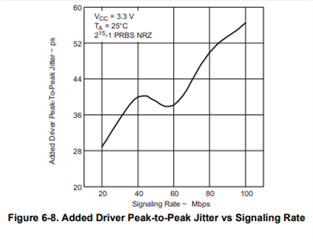

When input the clock to the SN65MLVD204A, is it possible to change jitter(tjit(pp))?

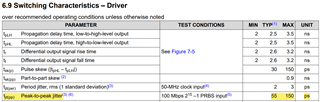

Driver spec on "9 Switching Characteristics" describes 55ps(TYP)、150ps(MAX).

For example, If SN65MLVD204A drives 10kHz clock(Duty50%) and 10MHz clock (Duty50%), does it causes the difference on jitter(tjit(pp)) of clock?

If yes, do you show the estimation for the difference on jitter(tjit(pp))?

In my opinion, the jitter might be change due to line impedance , the slope fo rising / falling edege and signal bit pattern chage the jitter.

Is it possible to estimate the tool like IBIS model?

SN65MLVD204A data sheet, product information and support | TI.com

Best Regards,

ttd