Tool/software:

We have developed an FMC card utilizing the TI TUSB1104 redriver for testing our USB 3.2 Gen 2x2 (10 Gbps per lane) IP core. The host platforms for this testing include high-speed FPGA boards from Xilinx, Altera (Intel), Lattice Semiconductor, and Asmedia.

Our objective is to pass USB compliance testing.

Observations in Pin-Strap Mode (Default Settings):

- Setup: Asmedia Type-C port + Amphenol cable

- Lane 1: Fails to enumerate, remains in Recovery state during enumeration.

- Lane 2: Successfully enumerates as USB 2.0, but does not achieve USB 3.2 operation.

Configuration & EQ Values Currently Used:

USB Connector Facing Port Receiver (CRX1, CRX2 pins) Equalization:

- EQ Gain at 5 GHz minus Gain at 100 MHz = 11.6 dB

USB Host Facing Port Receiver (SSTX1, SSTX2 pins) Equalization:

- EQ Gain at 5 GHz minus Gain at 100 MHz = 6 dB

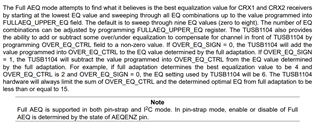

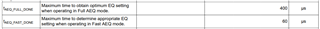

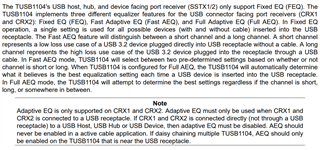

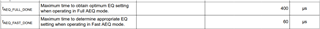

Full Adaptive Equalization (Full AEQ) Mode Consideration:

According to the TUSB1104 datasheet, when configured in Full Adaptive Equalization mode, the device autonomously determines the optimal equalization settings based on the signal channel characteristics. This mode dynamically adjusts the equalization for both short and long channels to optimize signal integrity.

We intend to use this mode for optimal performance.

The AEQCFG pin is currently set to 0x08 (floating in pin-strap mode), which enables Full Adaptive Equalization mode.

Request for Guidance:

We would like detailed instructions on properly utilizing Full AEQ mode, including:

- Confirmation of correct AEQCFG settings for optimal performance.

- Application guidelines or reference documentation from TI regarding Full AEQ mode implementation.