Tool/software:

We ran into an issue with the power-up sequence of the PHY DP83825I. In the Rev. B of the datasheet at “Figure 5-1. Power-Up- Timing” there is the information added: “Clock shall be available at Power Ramp. If not, hold RESET_N low and release it at least 100us after clock is stable.”

Investigations led to the assumption that our implementation of the PHY violates this obligation:

Firstly, we measured if XI is available at power ramp of VAVDD:

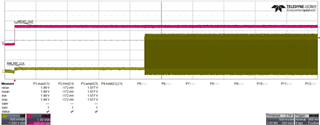

This picture shows the reset sequence of our SOM. VDD3V3A is connected to VAVDD and RMII_REF_CLK is connected to XI. As it can be seen the clock is not available at power ramp.

Secondly, we measured when the clock is stable in relation to our global reset-signal:

As it can be seen X_nRESET_OUT which is connected to RESET_N is not held low at least 100us after the clock is stable. RESET_N is controlled by a PMIC on our SOM, so the signal can’t be held down until the clock started because the clock is provided by the processor and the processor if affected by the reset-signal.

So the question is which problems can be caused by our implementation and if an additional software reset by MDIO-interface would be needed.