Other Parts Discussed in Thread: SN65DSI84

Tool/software:

I'm trying to connect 20.3" dual lvds lcd using SN65DSI85, so I have 2 questions.

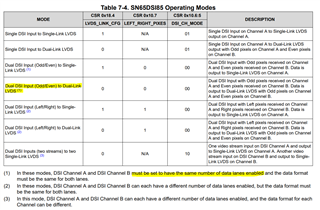

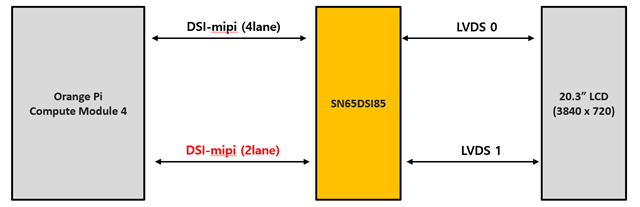

First, we will connect DSI mipi to 2ea in CM4 (Orange Pi Compute Module 4), and please review whether it is possible to drive 20.3" LCD when connecting 4lane 1ea and 2lane 1ea as shown below.

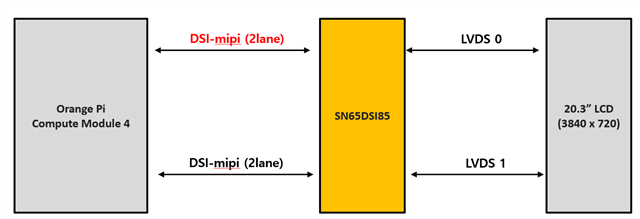

Secondly, I would like to ask you to review whether it is possible to drive 20.3" LCD when connecting 2lane 1ea and 2lane 1ea, but connecting 2lane 1ea.

Attached is a 20.3" LCD data sheet.