Tool/software:

hi Expert

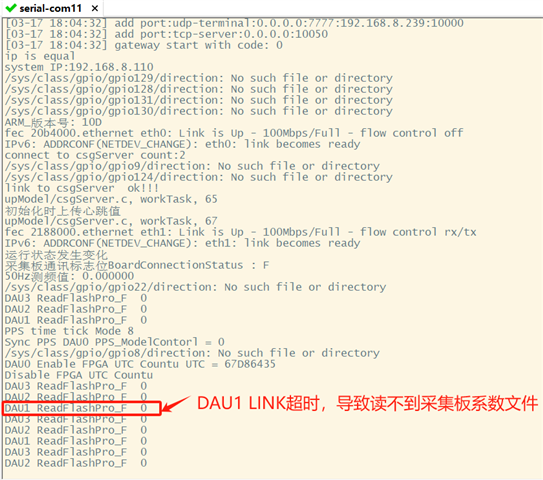

When using PHY chip DP83640 to power on, we may encounter a long LINK delay of the network port. PHY chip DP83640 on the acquisition board is not connected to the main control board in time for more than 3 seconds (Note: it can be linked eventually), resulting in the problem that the entire system cannot read the coefficient file of the acquisition board.

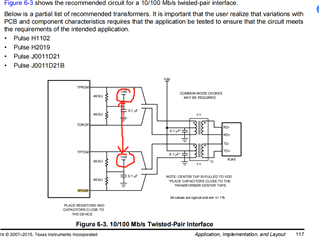

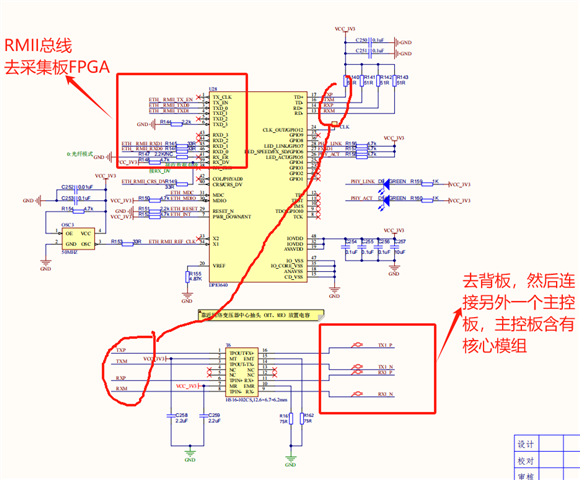

Here is our schematic diagram

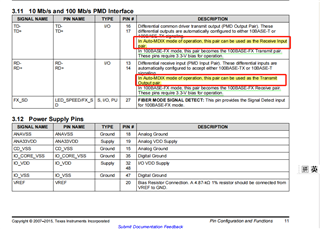

Note: ETH_RMII_CRS_DV, ETH_MDC, and ETH_MDIO all have no signals when they are powered on, and no signal is sent from the core board to the PHY chip. That is, the PHY chip needs to be configured automatically without the need for the core board to configure it.

The serial port displays the following information: When the board DAU1 LINK is powered on, you can see that the faulty board DAU1 Link times out, and the board coefficient file cannot be read.

For thsi question,could you help give me some advisers,Thanks a lot!