Part Number: BOOSTXL-CANFD-LIN

Other Parts Discussed in Thread: CC1310, TCAN4550

Tool/software:

Hello TI,

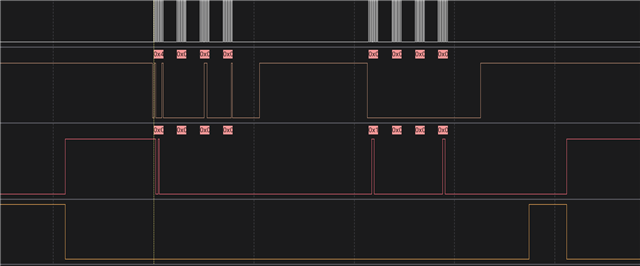

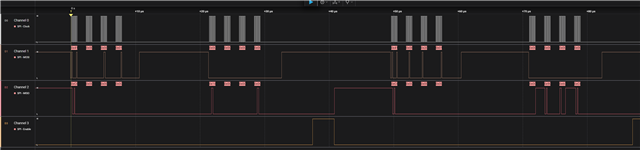

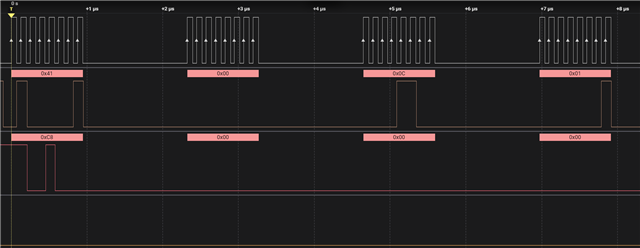

I am working on getting the TCAN4550 working on a SUB1 CC1310 microcontroller, and having trouble getting the CAN initialised. I believe the SPI is now correctly setup, with the following settings:

I am using the TCAN4550 demo software, in order to initialize the TCAN chip, but i am unable to write to the TCAN chip. During a read of the Error status register (0x000C) it reads the following:

0x18 0x00 0x00 0x0C which would mean there is a write error and an internal interrupt error.

I am unable to resolve this issue by looking at the data sheet, are there any steps i can take to debug the process?

This is a snapshot of the SPI communication.

Any help would be nice.

Kind regards