Part Number: DS90UB638-Q1

Tool/software:

We are testing 5 prototype systems with DS90UB635 / DS90UB638 pairs.

4 of them are performing well. One reports unstable Lock and Pass.

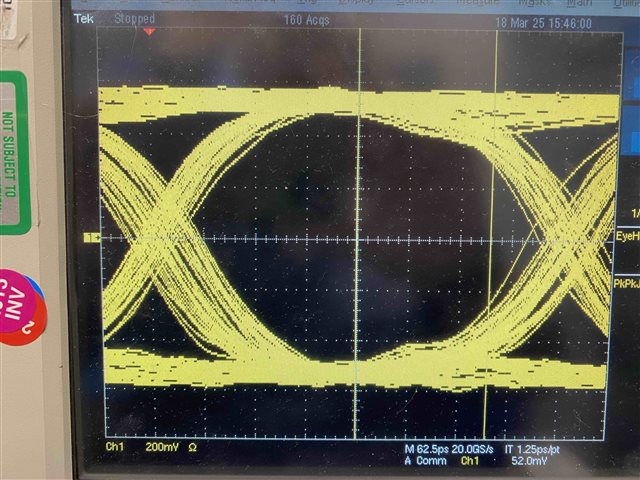

We enabled CMLOUT per the data sheet instructions and the eye diagram looks very good to me. We are connecting in twisted pair configuration, over a short link, in 2Gbps (half rate) mode.

It does not appear that the 638 registers support the necessary functionality for the "Margin Analysis Program" testing.

Can you offer any additional debugging techniques we might use to understand why Lock and Pass fail so frequently on this particular system?