Part Number: DP83869HM

Tool/software:

Hi everyone, we have produced a prototype that implements the PHY DP83869HM.

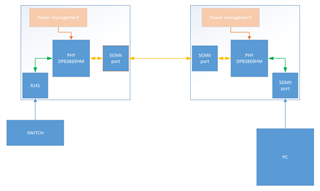

For testing we have connected two of them in a back-to-back SGMII configuration.

The SGMII link is shown below:

After powering up, everything seems to be normal. All voltages rails are ok.

The PHY seem to work. LED TX/RX blinking and Link up LED lit.

However, the PC cannot detect any connection with the LAN network.

I am wondering if there is a mistake in the SGMII wiring or maybe it is a mistake in the bootstrapping.

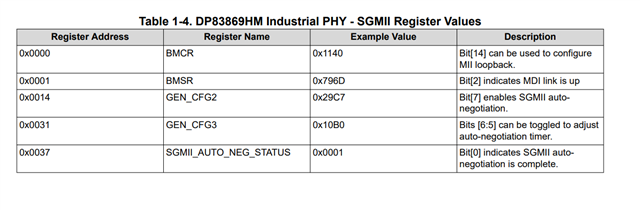

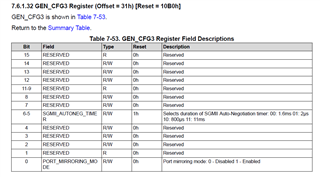

I have used the bootstrapping depicted here:

mirroring is disabled