Tool/software:

Hi,

In a current design I use the DP83822I physical in combination with the ESP32-MINI-1-N4. The PHY communicateds with the ESP32 over RMII.

However, on my proto types the RMII seems to have timing issues with the 50MHz clock and the TX and/or RX lines.

When I ping the IP adress the device occasionally pings correctly and occasionally gets a packet loss.

For each proto the occurence of packet losses differs.

One may never returns packet losses and the other always returns packet losses.

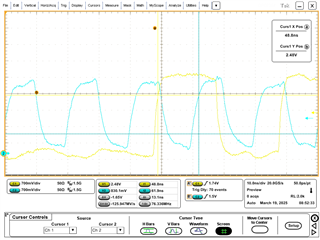

When I measure the timing on a scope the timing seems correct. See attached figures.

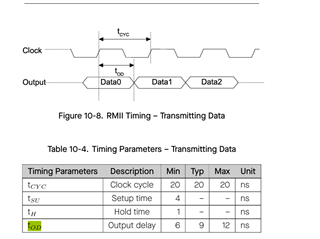

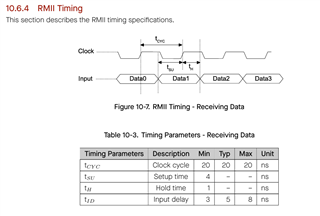

For receiving the setup time is 13ns and the hold is 7ns, and for transmission the setup is 10ns and the hold is 10ns aswell.

These values comply with the values provided in the data sheet.

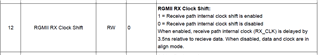

However the ESP32 technical reference manual introduses a input and output delay. These delays might be the cause of the issue, since they differ per module, which can make the timing critical.

Is there a way in software to add extra delay via registers on the 50MHz RMII clock or is it required to add a serial clock buffer to the 50MHz?