Tool/software:

Hi team,

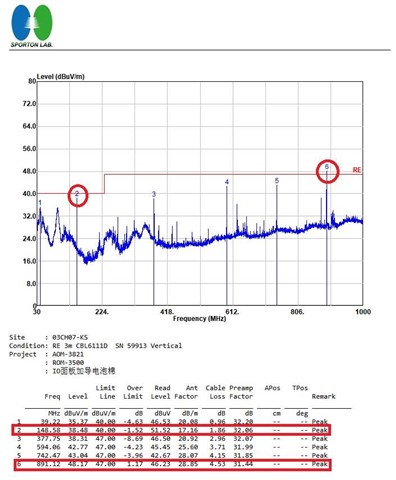

There is a project using TMDS181 in customer board. The HDMI points fail to meet the requirement of Class-B:

891MHz: over spec of 1.17dB

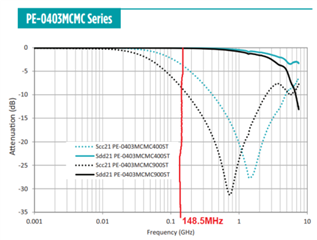

148MHz: the margin is only 1.52dB, which has risk.

Test results:

schematic:TMDS181 -AOM-3500_DCC SNOOP.pdf

layout: HDMI Re-timer-JOB.brd

Support need:

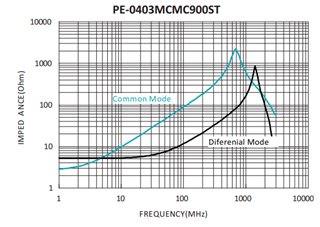

Help to suggest on how to improve the EMC performance. Whether it's related to the CMC choke selection?

BRs,

Rannie