Part Number: DP83867E

Tool/software:

Hello, we are using the DP83867E as a RGMII PHY connected to a Jetson AGX Orin and struggle to get a stable connection.

We have RX_CTRL strapped to Mode 3 and the remaining strap pins set to Mode 1.

During testing we have been able to get a network link by leaving the RESET_N pin disconnected from the Jetson PHY_Reset, and connecting the RESET_N pin to VDDIO through a RC circuit so that after a small delay the pin gets pulled up and stays high. With this setup we have verified that our hardware setup is correct, and we are able to have successful MDIO communication and internet connection.

When having the Jetson PHY_Reset connected we observe an issue where exchanging MDIO messages fails and the reset line gets pulled low by the Jetson.

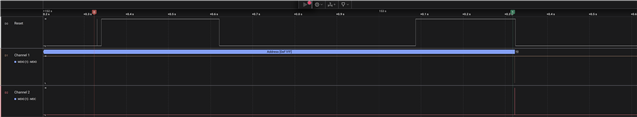

After connecting a logic analyzer, we are able to see the Jetson PHY_Reset behavior and MDIO packages. Marker 0 is where the reset sequence starts. Marker 1 is when MDIO communication is attempted.

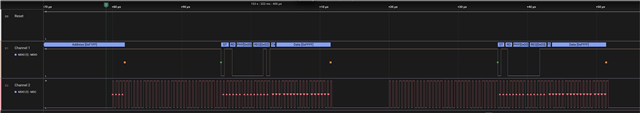

Zoomed in section of the attempted MDIO communication:

The Jetson attempts to read the registers 0x02 and 0x03, but the operation fails. The PHY does not pull down the MDIO line during turnaround and a value of 0xFFFFF is read, even though at that time the reset is high.

What could be causing this failure to read the MDIO data ?

Is it a viable approach to just have the RESET_N pulled up through a RC circuit and not connected to the Jetson ?