Part Number: THVD9491-SEP

Tool/software:

Hello

I am inquiring if I can receive the internal circuit diagram of THVD9491-SEP (RS-485 Transceiver).

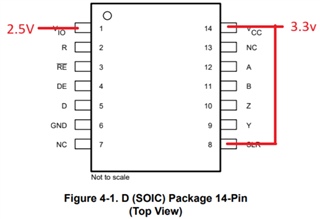

Currently, I have designed the circuit for THVD9491-SEP as follows. (Instead of the actual full circuit, I'm replacing it with a simplified image of just the power section)

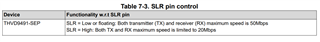

As you can see in the image, I've connected the SLR pin to the 3.3V VCC pin, and VIO is 2.5V.

The input voltage allowable range for the SLR pin is -0.3 < SLR < 2.7V (VIO+0.2).

Because I've exceeded the input voltage allowable range, it would be correct to change the design, but after checking the datasheet, I found out that the input voltage allowable range for the VIO pin is -0.5 < VIO < 3.5V (VCC+0.2).

Based on the situation, it seems that even if up to 3.7V is input to the SLR pin, there shouldn't be a major issue.

For this reason, I would like to request information about the chip's internal circuit to review whether there would be any issues with chip operation without changing the design.

Or if it's not possible, please let me know if it's not a big deal for the SLR Pin to be connected to 3.3V while VIO is 2.5V.

Sincerely,

MS Kim