Part Number: DP83867IS

Tool/software:

Our Ethernet connection block diagram is as follows. We connect the SGMII communication of the PHY on both sides through the connector.

However, occasionally, when disconnecting the connector and then connecting it again, the computers on both sides fail to establish Ethernet communication.

The DP83867 chip must be reset or the Ethernet cable between the PC and Phy must be re-plugged to restore communication. However, such a method requires at least 2~3 seconds to restore communication, and we want to be able to restore the link quickly.

We speculate that there may have been an anomaly in the clock synchronization when the SGMII interrupt was reconnected.

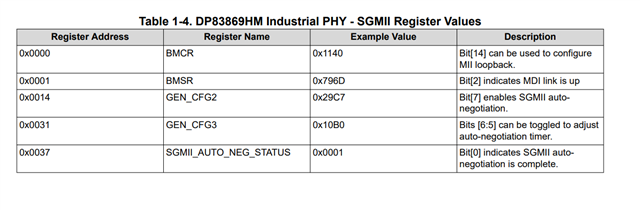

Can we read the connection status of the SGMII through the registers of the DP83867? Or can we manually control the PHY chip to do a link training without resetting the PHY chip? This may shorten the reconnection time.