Part Number: DP83822I

Tool/software:

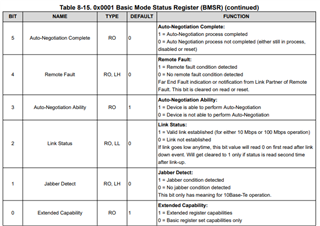

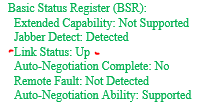

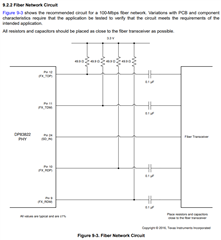

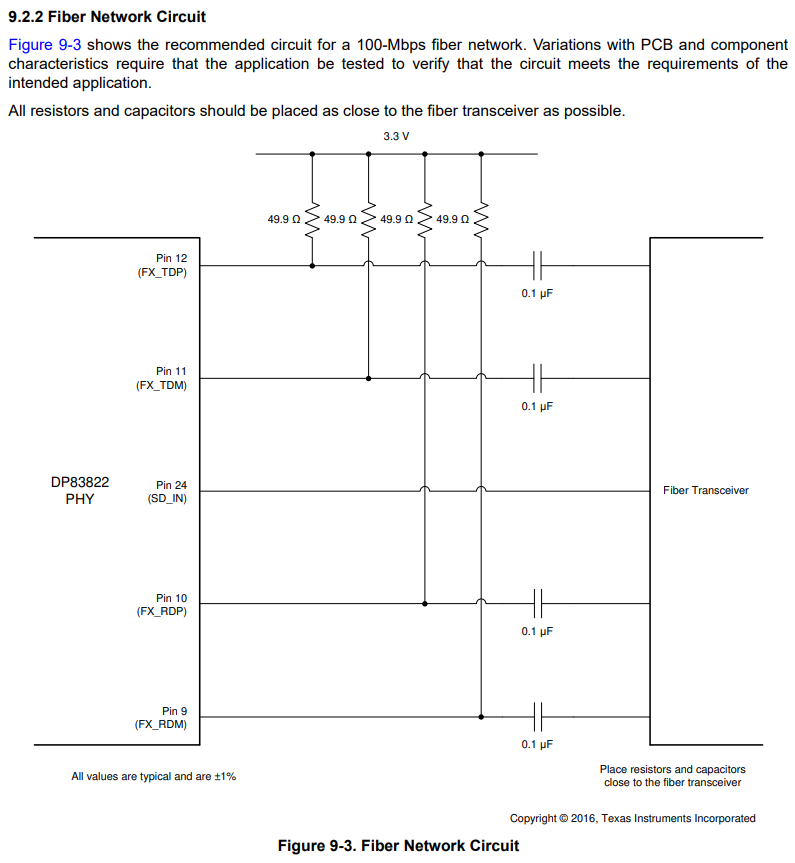

I integrated dp83822 PHY in a unit. The configuration is as follows: Duplex mode Full Duplex, Speed 100 Mbps, Auto-Negotiation Disabled, Loopback Disabled, Reset Inactive, Collision test Disabled. I also have the SD pin enabled. This unit directly interfaces with a fiber module. The fiber module interfaces with 10 other units. When I power up the system from cold and dark, I get a communication link error message from my system. The link error only happens to this units that has the DP83822 PHY. I power cycle the unit and the fault goes away (clears). The issue happens after about 4 and half minutes of the initial power up (it is consistently happening). The receive error counter and the false carrier error counters show higher count values right before the issue happens. The process I have during power up is: custom config gets loaded to the config register then I do a soft reset of the PHY and a reset of the clock. I would like to understand the root cause and address it accordingly. It would be really awesome if you can shed some light on this.