Part Number: DS90CR286A

Other Parts Discussed in Thread: TFP410,

Tool/software:

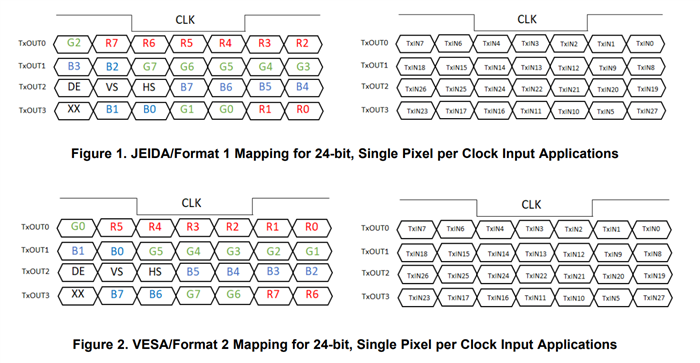

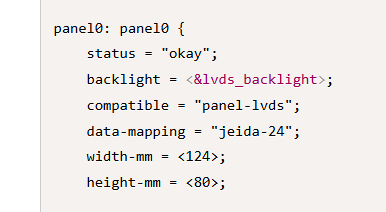

I have an NXP iMX9352 with integrated LVDS phy. The datasheet says it supports common display LVDS receivers which I assume are 24 bit VESA or JEIDA mapping.

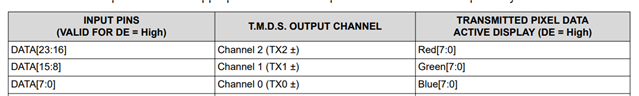

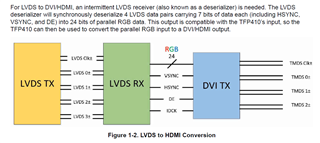

I am using the DS90CR286A to deserialize and the TFP410 to finally output TMDS lanes.

If the LVDS output already complies to a standard, and the TFP410 is my "RGB Receiver" then

Do I connect RX0-23 VSYC, HSYNC, and DE up to TFP410 input 0-26. in a 1:1 straight connection leaving RXout27 disconnected

OR

Do I need to connect RXout 27 to TFP410 input 23 to get R0/R6 bit, and leave RXout23 disconnected

The DS90CR286A is confusing me with the color mapping calling RXout23 as the general purpose bit.

Is the mapping already taken care of in the host processor output, or do I need to take care of it in Hardware traces between the deserializer and TFP410?

The app note for LVDS to HDMI is too vague.