Part Number: TCAN4550-Q1

Other Parts Discussed in Thread: TCAN4550EVM, TCAN4550

Tool/software:

Hello,

I am playing around with the TCAN4550EVM board, and have gotten SPI communication to work, where I can read and write the registers on the TCAN4550. However, I have been trying to put the chip in loopback mode so I can start pulling from the RX FIFO of the chip and processing messages, but have not succeeded in doing so. I just wanted to confirm my configuration and make sure I am not missing anything.

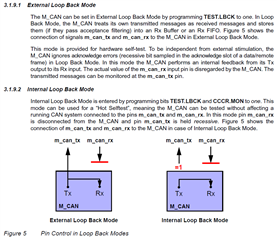

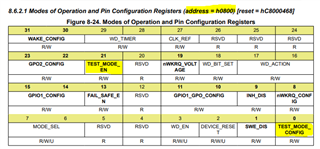

I am using the supplied software to configure the chip, including MRAM. Before the chip is put into normal mode I also configure the test register (0x1010) to enable loopback mode, and configure the cccr register (0x1018) to enable the MON bit, to disable external signals and only have internal loopback.

The TCAN4550 is put into normal mode.

The TCAN4550 is put into test mode using TCAN4x5x_Device_EnableTestMode(TCAN4x5x_DEVICE_TEST_MODE_CONTROLLER), and ensuring that the function returns true.

I then use the supplied software, lines 92-106 in main.c to write to the TX buffer, and line 129 to transmit the buffer. I know that up to this step it is working, because when not in loopback mode I get the message on the CAN bus. I also have verified that the correct data is getting written to the TX buffer.

However when trying to read the RX FIFO using lines 136-152 in main.c, the rx buffer is empty.

I have looked at the interrupts regsiter, and CANSLNT bit is set. Also in the mcan interrupts the TSW bit is set. Also in the SPI interrupts register bit 3, Internal_access_active, is high.

Please let me know if there is anything that I am doing wrong here. I'd really like to get internal or external loopback working on this chip.

Thanks,

Bennett