Other Parts Discussed in Thread: TSER953, DS90UB953-Q1, DS90UB960-Q1, TDES960

Tool/software:

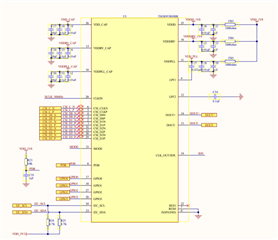

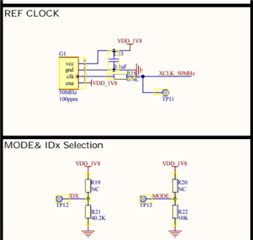

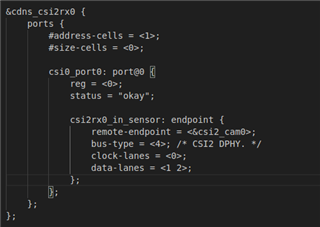

i try to set up new camera with uB960 and UB953. Here is the status below:

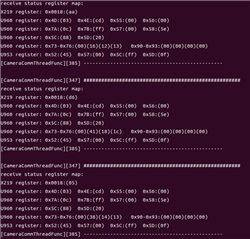

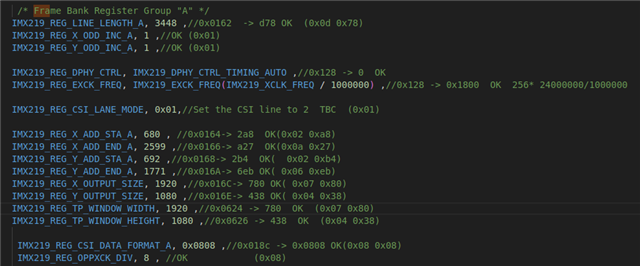

1. Sensor have correct config. and the sensor register "FrameCnt" changed after the register be read out. So video have be send out

2. read the GENERAL_STATUS register. The val is 0x45. It mean that the bit RX_LOCK_DETECT/HS_PLL_LOCK/LINK_DET was 1. this indicator the physical and config of 953 is correct implement

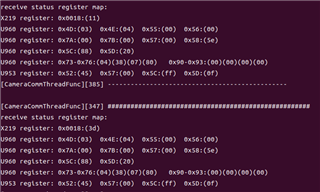

3. Read the CSI_RX_STS from 960. It show that the LENGTH_ERR and CKSUM_ERR. and by the way the Frame counter is 0 in 960 register and Image Line counter is wrong

Can you share me that the problem. and how i need to deal with this problem. thx