Part Number: SN65LVCP22

Tool/software:

Hi,

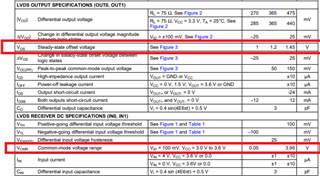

We are currently evaluating the SN65LVCP22 used as a 2:1 LVDS crosspoint switch in our system, and have observed unexpected output voltage behavior during SEL switching.

Configuration:

-

Device: SN65LVCP22

-

Usage: 2:1 LVDS switch (IN0 or IN1 to OUT based on SEL)

-

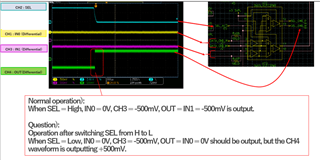

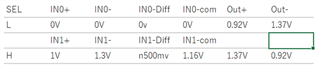

SEL = High: IN1 → OUT

-

SEL = Low: IN0 → OUT

-

Both IN0 and IN1 receive AC-coupled LVDS signals from other devices.

Observed Issue:

When switching SEL from High to Low to route IN0 to the output, we observe +500mV at the output even though IN0 is at 0V (no signal).

However, when both IN0 and IN1 are at -500mV, switching SEL results in the expected -500mV at the output.

Our Understanding:

We believe this behavior is not a device failure, but may relate to one of the following:

-

IN0 may be in a High-Z state during SEL transition, and the output reflects an internal bias voltage (~+500mV).

-

The device may produce undefined output voltage if switching occurs while the input is not actively driven.

-

Lack of termination or pull-down on a floating input might be causing this behavior.

We would appreciate it if you could advise whether this output behavior is expected under the above conditions, and whether there are any recommended countermeasures (e.g., input biasing, termination guidance, or switching timing considerations).

Thanks,

Conor