Part Number: SN65DPHY440SS

Tool/software:

Hi,

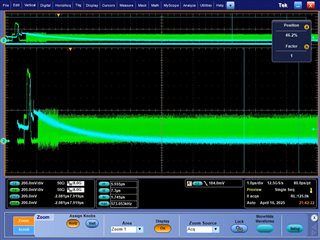

I am designing a camera board with a 300mm long FPC. Considering length of the FPC, a SN65DPHY440SS is added. When PCB and FPC are back, I found no MIPI CSI transmission at all. During debug, I can see MIPI CSI signals on input side of SN65 BUT no output waveform at all. See below waveform, the green signals which is measured at input port of SN65 IC, LP and HS signals can be identified. But the blue one, which is measured at output side of IC, HS signal is almost zero.

Another test was also performed by removing the SN65 IC and directly connecting input pad and output pad on PCB. MIPI CSI was working good then.

Could you please help to provide some ideas on this? Thx a lot in advance.