Tool/software:

Hi team,

[Problem]

My customer is facing issue that MDIO can't be accessed sometimes for only single sample out of 50pcs. The issue happened 1~2 times out of 10 times power cycles for the unit.

There is no response to the MDIO access when the issue occurs, and the register value cannot be read. (It has been confirmed with a waveform that there is no response.)

Performing a hardware reset when the issue occurs allows MDIO access.

[Assumption]

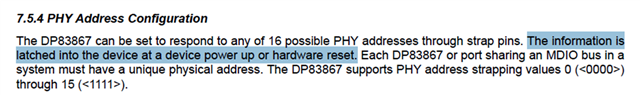

He doesn't think the issue cause by PCB because it recovers by hardware reset. He doubts incorrect strap setting which leads to wrong PHY address setting when power-on.

[Question]

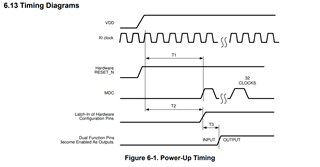

The datasheet states "The information is latched into the device at a device power up or hardware reset".

For now, the device starts up with RESET_N Low when power-on. Then, RESET_N is released after more than 500ms.

Is powering up with remaining RESET_N Low compliant to below condition for latching properly?

Best regards,

Shota Mago