Part Number: TIC12400-Q1

Tool/software:

Hello team,

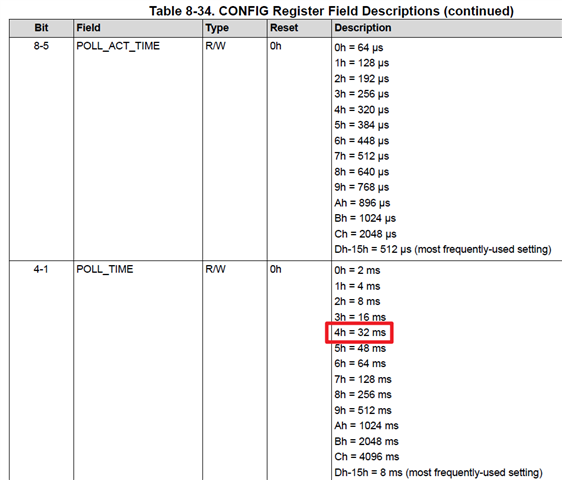

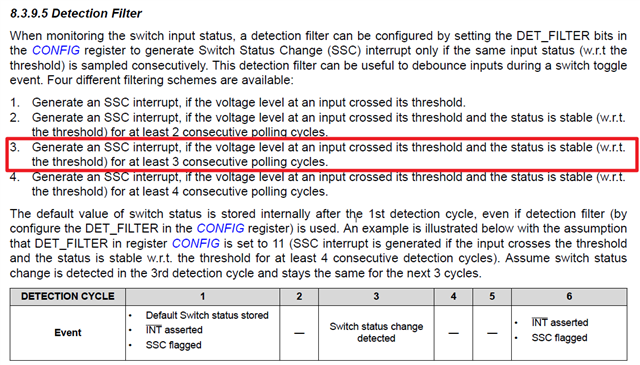

Customer configured the POLL_TIME as 32ms, detection filter configured as least consecutive polling cycles, here are two questions to confirm with you:

1. Will the register SSC be refreshed every 96ms (32ms *3)?

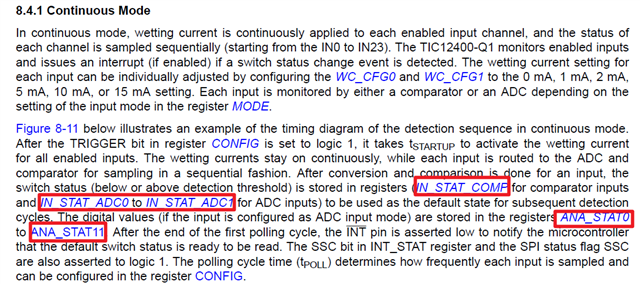

2. How about the DI and ADC registers including IN_STAT_COMP,IN_STAT_ADC0 to IN_STAT_ADC1,ANA_STAT0 to ANA_STAT11, will them be refreshed every 32ms or 96ms?

Thanks!

Regards,

Daniel Wang