Other Parts Discussed in Thread: TPS65994,

Tool/software:

Hello Team,

I have an issue that customer uses our Type-C PD controller TPS65994 with USB3.2 gen2x2 redriver TUSB1104 at their system.

I set this in public because the customer would also like to track this issue.

The data of the USB-C port is only being capable of USB3.2 gen2x2, no DP and TBT is needed.

The result is that the port 2 cannot be linked at 3.2 gen2x2, but port one is ok. Both port setting are the same, this is quite weird.

I only do the following things through I2C communication:

1. Power on/reset: write 0x11 to 0x0A (general register)

2. Detach: write 0x11 to 0x0A

3. Upside up attach: 0x11 to 0x0A

4. Upside down attach: 0x15 to 0x0A

Which means all the EQ setting is based on adaptive EQ default setting.

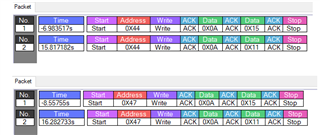

Here's the I2C3 log: (0x44 address for port 1, and 0x47 for port 2)

I think the communication between PD and SoC and redriver should be OK.

Here's what I found strange, please see the orange circle here, I upside-down attach the device, and the 0xA seems to be correct(15 in register).

But the USB1/USB2 status' bit 0 is still asserted, which means the device is disconnected, is this why the port 2 always being fail?

Best regards,

Dave