Other Parts Discussed in Thread: AM2634, , DP83822I, DP83822EVM, DP83869

Tool/software:

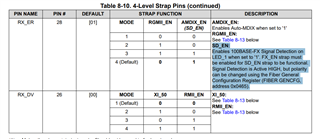

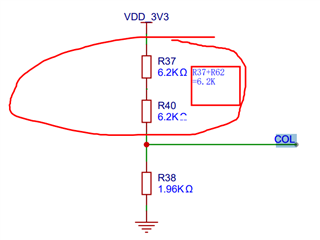

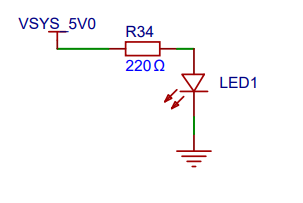

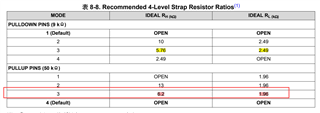

Hello, expert. I am using DP83822IF 100 BASE-FX to connect to the switch and finally connect to the computer. Between DP83822IF and the switch, two 155M SFP 1310nm 20km SM/LC modules are used to connect with two LC optical fibers. And the SD pin of the SFP module was connected to LED_1 / GPIO1 of DP83822. Now the loopback test between MCU AM2634 and PHY can be completed without errors. Meanwhile, when I plug or unplug any optical fiber, Both the link LED of the switch and the LED_0 of DP83822 can correctly indicate the disconnection and connection of the link.

However, when I run the APP program, the program shows that the link status of Bit 2 in Register 0x0001 is always 0, causing the program to be unable to establish a connection all the time. Where might the problem be?