Part Number: DP83822IF

Other Parts Discussed in Thread: DP83822EVM

Tool/software:

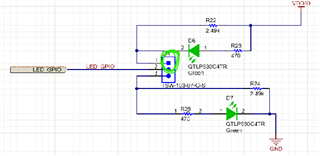

Hi,

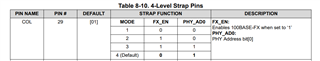

we are using DP83822IF in a SFP config. we are having a problem establishing a link through SFP, when we read back the registers we get the wrong values although they are set by a hardware straps.

also we ran a self test/ loopback test and came back w/o errors.

we started to follow the DP83822 Troubleshooting Guide.

In normal operation:

we found the the Vrbias = 0.987V Not the recommended 2.7V

Pin COL = 0.0280V instead of ~ 0.8V

Pin RX_DV = 0.0280V instead of ~ 0.8V

the Values are right in just two case when the IC itself is removed from the PCB or the reset line is LOW.

what we already tried:

1. replacing DP83822IF.

2. checking AVD & VDDIO voltages and replacing the ferrite beads w/ 0R.

3. checking all the resistor values on the PCB.

3. Pullup resistor 2.21K on the MDIO W.R.T VDDIO.

Could you please take a look at the Schematics and see if their is something missing or wrong?

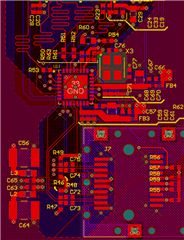

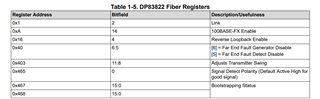

you can find the attached Schematics with the Hardware strap config at the top.