Part Number: SN65DSI86

Tool/software:

Hello everyone, We are converting the RGB signal from an STM32F429 via a Toshiba RGB/DSI TC358778XBG bridge in order to convert it to DisplayPort via the SN65DSI86 bridge.

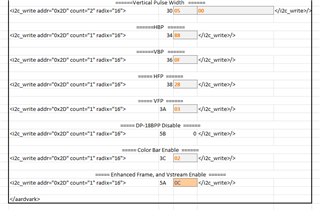

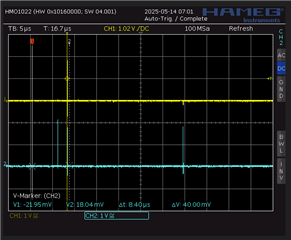

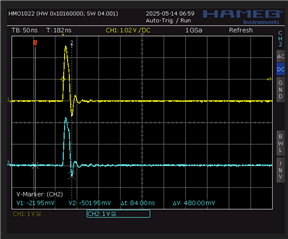

When we test the timings we set with the test image of the SN65DSI86, the monitor works. If we turn off the test image with the same settings and try to display

the STM32 image on the monitor, we get the error message LOSS_OF_DP_SYNC_LOCK_ERR.

All attempts with changed resolutions and timings repeatedly result in this error.

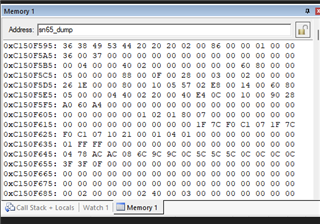

We also noticed that the MVID register (0x40...0x42) fluctuates considerably, even in the high byte.

Can anyone help us? What is a possible cause?

Regards Thomas