Tool/software:

I am not able to configure auto negotiation for 10 and 100 mbps by strap pins. please Give me a proper steps to set auto negotiation for 10 and 100 mbps RGMII mode.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I am not able to configure auto negotiation for 10 and 100 mbps by strap pins. please Give me a proper steps to set auto negotiation for 10 and 100 mbps RGMII mode.

Hi,

Please use the attached spreadsheet for the DP83867E strap configuration.

Thanks

David

Hi David,

1) I have configure phy for auto negotiation using strap pins as per sheet given by you.i required strap configuration for 10 and 100 mbps RGMII mode because i am using 2 wire interface between phy ic and connector.

2) when i read phy status reg it is showing that link is down.

3) so am i need to set registers by mdio. If yes then please give me all steps to configure register to set auto negotiation 10 and 100 MBPS RGMII mode.

Thanks,

Prasad

Hi David,

Please check Attached Hardware schematic. Do i need any change in strap pin configuration for auto negotiation for 10 and 100 Mbps RGMII mode.

Thanks,

Prasad

Prasad

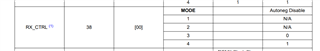

The strap configuration on the RX_CTRL pin controls the auto-negotiation enable and disable. You have to set the RX_CTRL pin to Mode 3 to disable and Mode 4 to enable auto-negotiation.

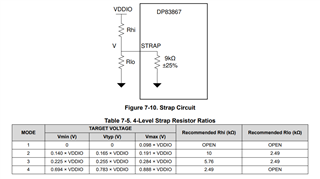

To enable auto-negotiation, pullup is 5.76k and pulldown is 2.49k. I noticed in your schematic you have a 6.04k pullup, can you please change it to 5.76k?

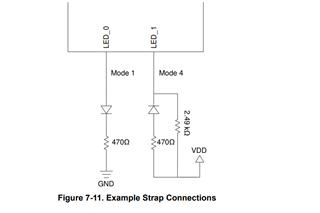

The LED_1 selects Auto-Negotiation Advertisement between 10/100/1000 and 100/1000. For 10/100/1000 advertisement, LED_1 strap mode is Mode 1 which is open. Please see below for the LED Mode 1 implementation. I noticed in your schematic the LED diode and 470ohm resistor is swapped and this needs to be fixed.

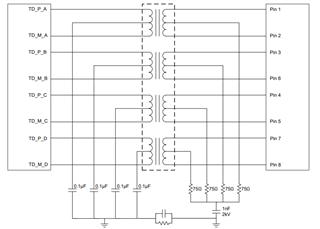

Also looking at the integrated transformer and RJ45, you have the center tap shorted together and then pulled to ground through 0.01uF capacitor. We recommendation to keep each center tap on the side connected to the PHY be isolated from one another and connected to ground via a decoupling capacitor (0.1µF recommended) as shown below.

Can you also dump out extended register 0x6E and 0x6F? This will verify the strap configuration is being done correctly.

Thanks

David

Dear David,

Please tell me how to set the RX_CTRL pin to Mode 3 to disable and Mode 4 to enable auto-negotiation. i have did other changes changes as you mentioned previously.

Thanks,

Prasad

Dear David,

1) Please tell me how to set the RX_CTRL pin to Mode 3 to disable and Mode 4 to enable auto-negotiation. Because as per you shared spreadsheet for the DP83867E strap configuration in that same configuration suggested i.e. pullup is 5.76k and pulldown is 2.49k. I have done other changes as you mentioned previously.

2) Apart from auto negotiation set by strap pins do i need to set Registers for 10 and 100 MBPS RGMII Auto Neg. by software(MDIO).If yes then please suggest me which registers i need set for it.

Thanks,

Prasad

Prasad

To enable auto-negotiation, strapping RX_CTRL pin to Mode 3 -> 5.76k pullup and 2.49k pulldown.

To disable auto-negotiation, strapping RX_CTRL pin to Mode 4 -> 2.49k pullup, and open pulldown.

Once the PHY is configured to have auto-negotiation enabled, it will automatically start the auto-negotiation as soon as the link is established with its link partner. There is no need to configure auto-negotiation through the MDIO bus.

Thanks

David

David,

My question is how to enable mode 4 and how to disable mode 3, but you given reverse answer because in previous discussion you suggested that i need to set mode 4 for 10 and 100 MBPS Auto Neg.

Thanks,

Prasad

Prasad

I apologize, this was a typo in my response. You have to use pin strap to enable/disable Auto-Negotiation.

To enable auto-negotiation, strapping RX_CTRL pin to Mode 3 -> 5.76k pullup and 2.49k pulldown.

To disable auto-negotiation, strapping RX_CTRL pin to Mode 4 -> 2.49k pullup, and open pulldown.

If Auto-Negotiation is disabled by strap option, Auto-Negotiation can not be reenabled by the MDIO.

Thanks

David

Hi David,

1) I am using sja1105Q switch(MAC) where i have set it as a 100 MBPS RGMII Mode (Static config).

2) Now i have set DP83867E(PHY) as enable auto-negotiation, strapping RX_CTRL pin to Mode 3 -> 5.76k pullup and 2.49k pulldown.

i am getting output as:

PHY_ADDR 0 BMSR (0x0001): 0x7949

PHY_ADDR 0 phy sts (0x0011): 0x0302

PHY_ADDR 3 BMSR (0x0001): 0x7949

PHY_ADDR 3 phy sts (0x0011): 0x0302

So what may be the issue for it. please let me know the is my auto negotiation is complete properly or not or what steps i need to follow to resolve the issue.

Thank You

Prasad

Prasad

Register 0x0001 shows a value of 0x7949, so AUTO-NEGOTIATION is enabled but not completed, and link is not established for both PHY0 and PHY3.

Can you please dump out register 0x0000 to 0x001F, 0x006E and 0x006F?

Also, can you read register 0x0031 bit 0? If bit 0 is set (mirror mode enabled), can you please write a 0 to it and see if you are able to get link up?

Thanks

David

Hi David,

please check all register value for 2 ports.

PHY_ADDR 0 Reg 0x0000: 0x1140

PHY_ADDR 0 Reg 0x0001: 0x7949

PHY_ADDR 0 Reg 0x0002: 0x2000

PHY_ADDR 0 Reg 0x0003: 0xA231

PHY_ADDR 0 Reg 0x0004: 0x0181

PHY_ADDR 0 Reg 0x0005: 0x0000

PHY_ADDR 0 Reg 0x0006: 0x0064

PHY_ADDR 0 Reg 0x0007: 0x2001

PHY_ADDR 0 Reg 0x0008: 0x0000

PHY_ADDR 0 Reg 0x0009: 0x0300

PHY_ADDR 0 Reg 0x000A: 0x0000

PHY_ADDR 0 Reg 0x000B: 0x0000

PHY_ADDR 0 Reg 0x000C: 0x0000

PHY_ADDR 0 Reg 0x000D: 0x0000

PHY_ADDR 0 Reg 0x000E: 0x0000

PHY_ADDR 0 Reg 0x000F: 0x3000

PHY_ADDR 0 Reg 0x0010: 0x5048

PHY_ADDR 0 Reg 0x0011: 0x0002

PHY_ADDR 0 Reg 0x0012: 0x0000

PHY_ADDR 0 Reg 0x0013: 0x0000

PHY_ADDR 0 Reg 0x0014: 0x29C7

PHY_ADDR 0 Reg 0x0015: 0x0000

PHY_ADDR 0 Reg 0x0016: 0x0000

PHY_ADDR 0 Reg 0x0017: 0x0040

PHY_ADDR 0 Reg 0x0018: 0x6150

PHY_ADDR 0 Reg 0x0019: 0x4404

PHY_ADDR 0 Reg 0x001A: 0x0002

PHY_ADDR 0 Reg 0x001B: 0x0000

PHY_ADDR 0 Reg 0x001C: 0x0000

PHY_ADDR 0 Reg 0x001D: 0x0000

PHY_ADDR 0 Reg 0x001E: 0x0002

PHY_ADDR 0 Reg 0x001F: 0x0000

PHY_ADDR 0 Reg 0x006E: 0x0000

PHY_ADDR 0 Reg 0x006F: 0x3000

PHY_ADDR 3 Reg 0x0000: 0x1140

PHY_ADDR 3 Reg 0x0001: 0x7949

PHY_ADDR 3 Reg 0x0002: 0x2000

PHY_ADDR 3 Reg 0x0003: 0xA231

PHY_ADDR 3 Reg 0x0004: 0x0181

PHY_ADDR 3 Reg 0x0005: 0x0000

PHY_ADDR 3 Reg 0x0006: 0x0064

PHY_ADDR 3 Reg 0x0007: 0x2001

PHY_ADDR 3 Reg 0x0008: 0x0000

PHY_ADDR 3 Reg 0x0009: 0x0300

PHY_ADDR 3 Reg 0x000A: 0x0000

PHY_ADDR 3 Reg 0x000B: 0x0000

PHY_ADDR 3 Reg 0x000C: 0x0000

PHY_ADDR 3 Reg 0x000D: 0x0000

PHY_ADDR 3 Reg 0x000E: 0x0000

PHY_ADDR 3 Reg 0x000F: 0x3000

PHY_ADDR 3 Reg 0x0010: 0x5048

PHY_ADDR 3 Reg 0x0011: 0x0302

PHY_ADDR 3 Reg 0x0012: 0x0000

PHY_ADDR 3 Reg 0x0013: 0x0040

PHY_ADDR 3 Reg 0x0014: 0x29C7

PHY_ADDR 3 Reg 0x0015: 0x0000

PHY_ADDR 3 Reg 0x0016: 0x0000

PHY_ADDR 3 Reg 0x0017: 0x0040

PHY_ADDR 3 Reg 0x0018: 0x6150

PHY_ADDR 3 Reg 0x0019: 0x4404

PHY_ADDR 3 Reg 0x001A: 0x0002

PHY_ADDR 3 Reg 0x001B: 0x0000

PHY_ADDR 3 Reg 0x001C: 0x0000

PHY_ADDR 3 Reg 0x001D: 0x0000

PHY_ADDR 3 Reg 0x001E: 0x0002

PHY_ADDR 3 Reg 0x001F: 0x0000

PHY_ADDR 3 Reg 0x006E: 0x0000

PHY_ADDR 3 Reg 0x006F: 0x3000

also, I have read Register 0x0031 getting value 0x302 means no port mirroring enable.

Thanks,

Prasad

Hi Prasad,

David is currently out of town so I will take over this case.

Based on the register dump, register 05h is 0x00. This shows that the PHY doesn't recognize the link partner's advertisement on 100BASE-TX (bit 7 and 8).

Could you try enabling auto-negotiation for 10/100/1000Mbps and see if the PHY can link up with the link partner?

Best,

J

Hi J,

As previous discussion with david that i am using 2 pair communication between phy and connector. I want to use auto negotiation for 10 and 100 MBPS by strap pins. as per the dump out register value do i need to do changes in hardware strap pins for 100 and 10 MBPS Auto negotiation. Because David suggests me if auto negotiation done by strap pins then no need to configure phy by MDIO.

Also my Question is as per datasheet phy uses IEEE 802.3u and switch(SJA1105Q) has IEEE 802.3 protocol but support 10,100,1000 mbps speed.is there any issue occurs due to Difference in protocol.

Please help me to Resolve this Issue its very critical for us now.

Thanks,

Prasad

Hi Prasad,

Also my Question is as per datasheet phy uses IEEE 802.3u and switch(SJA1105Q) has IEEE 802.3 protocol but support 10,100,1000 mbps speed.is there any issue occurs due to Difference in protocol.

802.3u is a subset of 802.3 so there will be no issue.

I apologize for the confusion but our strap options support auto-negotiation for 10/100/1000 OR 100/1000. We do not have a strap option for 10/100 advertisement only.

To support 10 and 100 only, you would have to enable 10/100/1000 on strap and disable bit 9 and 8 of the register 0x0009. Currently, your register dump shows that register 0x0009 is 0x0300 meaning those bits are on.

Best,

J

Hi Prasad,

As David said, strapping LED_1 pin to Mode 1 or 2 (depending on your preference on the RGMII TX Clock Skew) will select auto-negotiation advertisement to 10/100/1000.

Enabling auto-negotiation itself is controlled by RX_CTRL pin and strapping that to Mode 3 will enable auto-negotiation.

Your register dump already shows that auto-negotiation is enabled (bit 12 of register 0x0000 is 1).

But it looks like auto-negotiation wasn't completed so link is not established.

Please follow this table for recommended resistor settings:

Best,

J

Hi J,

Now My Hardware is working fine thanks for your help.

Currently i am doing Loop Back test (ANALOG, DIGITAL, PCS) for phy but its not working.

i have follow the guideline given by TI as Follow:

Note: i have test this code for 10 and 100 MBPS simultaneously.

code:

mdio_write(phy_addr, 0x001F, 0x8000);

HAL_Delay(100);

// Step 2: Disable Auto-Negotiation, Force 10 Mbps

mdio_write(phy_addr, 0x0000, 0x0100); // (1) speed select

// Step 3: Enable Analog Loopback (assumes default)

mdio_write(phy_addr, 0x0016, 0x0003); // (2) digital loopback

// Step 4: Force MDI mode (for 10/100 Mbps)

mdio_write(phy_addr, 0x0010, 0x5008);

// Step 5: Configure loopback register

mdio_write(phy_addr, 0x00FE, 0xE720);

HAL_Delay(10);

// Step 6: Enable packet generation, keep analog loopback

mdio_write(phy_addr, 0x0016, 0x5003); // (3) packet gen + digital loopback

HAL_Delay(1000); // Wait for PRBS to send packets

// Lock byte count

mdio_write(phy_addr, 0x0072, 0x0201);

// Read lock status, packet count, and error count

uint16_t lock_status = mdio_read(phy_addr, 0x0017);

uint16_t packet_count_1 = mdio_read(phy_addr, 0x0071);

uint16_t error_count = mdio_read(phy_addr, 0x0072);

// Enable continuous counting

mdio_write(phy_addr, 0x0016, 0xD004);

// Update packet counter

mdio_write(phy_addr, 0x0072, 0x0201); // (4)

uint16_t packet_count_2 = mdio_read(phy_addr, 0x0071); // (5)

HAL_Delay(1000); // Optional: repeat to observe counter increment

mdio_write(phy_addr, 0x0072, 0x0201);

uint16_t packet_count_3 = mdio_read(phy_addr, 0x0071);

// Optional soft reset

mdio_write(phy_addr, 0x001F, 0x4000);

// Display results

printf("PHY Addr: 0x%02X\n", phy_addr);

printf("PRBS Lock Status: 0x%04X\n", lock_status);

printf("Initial Packet Count: %u\n", packet_count_1);

printf("Updated Packet Count: %u\n", packet_count_2);

printf("Final Packet Count: %u\n", packet_count_3);

printf("Error Count: %u\n", error_count);

if (lock_status & (1 << 11)) {

printf("PRBS test successful.\n");

} else {

printf("PRBS test failed.\n");

}

OUTPUT:

PHY Addr: 0x00

PRBS Lock Status: 0x0000

Initial Packet Count: 2

Updated Packet Count: 2

Final Packet Count: 2

Error Count: 513

PRBS test failed.

Please let me know where i am doing wrong steps.

Thanks,

Prasad

Hi Prasad,

What is the test setup here?

Are you putting the same PHY in loopback mode and generate PRBS packets?

Please let me know.

Best,

J

Hi Prasad,

On-chip PRBS packet generation will not be measured by internal loopback modes.

What exactly is the problem you are facing that you had to do the loopback mode?

Best,

J

Hi Prasad,

You are correct to use the loopback mode.

You can have a tester send packets to the PHY and the PHY can loop back those packets. You can check on the link partner to see if there are any packet errors this way.

Please let me know if you have any questions about this.

Best,

J