Part Number: DP83825I

Tool/software:

I want to ask a question about power-up sequences.

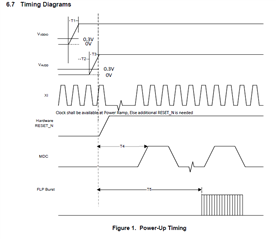

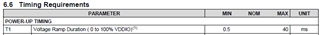

According to the data sheet, T1 requires more than 0.5 ms, but note (1) says "If Clock is provided after power ramp, external Reset of PHY is needed once clock is available".

Is this correct to say that the reset should be in effect for a while after VDDIO has been ramped?

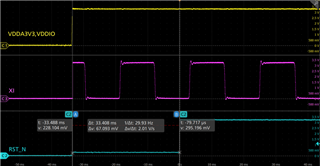

In our prototype board, the power-up sequence is shown in the figure, with the reset being released 33ms after the power supply is turned on.

I would like advice on whether this behavior is a problem.

Best regards.