Part Number: DS280DF810

Tool/software:

Hi,

We use the DS280DF810 with the EEPROM design in our project, and the 25Gbps design is OK,

Now we have below issue for 10Gbps design:

1. This 25G network card will be compatible with 10G usage in the future, but I don't want to burn the EEPROM again. Now there is a solution that needs to be confirmed with TI to see if it is feasible.

The specification sheet says that DS280DF810 will access from different starting bits of EEPROM based on different I2C addresses.

I am planning to revise it by switching the I2C address of the retimer chip to achieve two I2C addresses corresponding to different rates on one chip. Can EEPROM package all parameters of both rates?

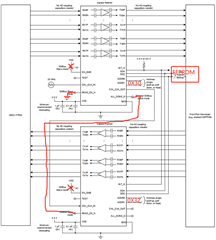

2. We also need to design this 100G card, which will use two DS280DF810 cards. Could you please help confirm the specific wiring method?

The block diagram on the specification sheet uses EEPROM mode, and the two retimers share the crystal oscillator and EEPROM according to the wiring method shown in the figure below.

Also, if the parameters used by the two retimers are the same as those of the 25G network card, can they share the same version of EEPROM as the first point 25G/10G network card?