Tool/software:

Hello everyone.

We are experiencing an LCD syncrhonization issue that causes LCD flickering or no video on an LVDS LCD screen, depending on the display timing configuration.

The application is converting the MIPI-DSI signal from an i.MX 8M Mini processor to the SN65DSI84 LVDS bridge on a VAR-SOM-MX8M-MINI Variscite SOM. It works with some LCD displays, but we are unable to configure the interface in a way that precisely matches the device tree.

The I2C registers are all verified against the given device tree panel section. The test pattern works without any issue just by setting CHA_TEST_PATTERN (any other register gets configured at drive probe phase).

The application uses a single DSI channel, 4 lanes, and a single LVDS output, RGB888.

We already asked for help about the configuration of the MIPI-DSI side on the SOC manufacturer's forums. But here we hope to get some suggestions about what could cause the issue on the bridge side.

The LCD is a 1280x800px with a pixel clock set at 72.4MHz.

Register settings

- ACTIVE_LINE_LENGTH: 1280 / 0x500

- VERTICAL DISPLAY SIZE: 800 / 0x320

- SYNC_DELAY: 33 / 0x21

- HSYNC_PULSE_WIDTH: 40 / 0x28

- VSYNC_PULSE_WIDTH: 15 / 0x0F

- HORIZONTAL_BACK_PORCH: 40 / 0x28

- VERTICAL_BACK_PORCH: 14 / 0x0E

- HORIZONTAL_FRONT_PORCH: 80 / 0x50

- VERTICAL_FRONT_PORCH: 9 / 0x09

This is the I2C dump:

~#i2cdump -y -f 0 0x2c

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 35 38 49 53 44 20 20 20 01 00 85 10 00 01 00 00 58ISD ?.??.?..

10: 26 00 2c 00 00 00 00 00 18 05 03 00 00 00 00 00 &.,.....???.....

20: 00 05 00 00 20 03 00 00 21 00 00 00 28 00 00 00 .?.. ?..!...(...

30: 0f 00 00 00 28 00 0e 00 50 00 09 00 00 00 00 00 ?...(.?.P.?.....

The DSI Tuner matches the configuration in Device Tree, except we're trying to locate the information about the MIPI-DSI clocks that seems automatically generated by the driver but they are not reported in the clock tree.

We deserialized the LVDS signals, and we discovered that:

- The LVDS clock exactly matches the pixel clock frequency

- Horizontal and vertical pulse witdh are the same as configured in DT

- Horizontal and vertical back porch timings are as configured, together with vertical front porch

- Horizontal front porch timing is NEVER respected, even when a certain configuration works, it's because the output is within the LCD tolerance.

- By slightly changing the configuration (basically the LCD clock or some the other timings, still within LCD tolerances) we experienced unpredictable changes on the LCD signals, up to the VSYNC pulse disappearing completely.

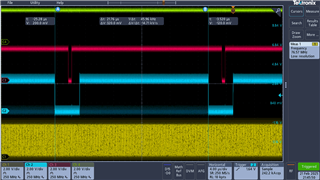

Just as an example, in the following diagram the blue line (C2) is the DE signal, while the red (C3) is HSYNC.

HFP has been programmed to 48, HBP to 80. HBP is respected, while we measure HFP to be around 135 pixel clocks instead of 48.

Siince the Linux driver is taking care of configuring both the LVDS and the MIPI-DSI timings, we kindly ask if anyone ever experienced the same issue, or if you have hints on what could cause it or where we should investigate.