Part Number: TCAN4550

Tool/software:

Hi Ti team,

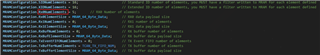

I would like to ask how many Rx0NumElements should be set appropriately in the configuration of TCAN4550, because I found that when it is configured to 32, the packet receiving rate can only run for a period of time when it is too fast, and then it cannot receive packets normally.