Tool/software:

Hi team,

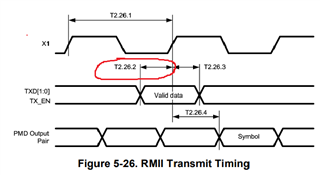

My customer is testing DP83848C on their PCB. They found a problem: the RMII transmit timing of their MAC cannot meet the requirements of DP83848. The "TXD[1:0], TX_EN, Data setup to X1 rising time" is required 4ns minimum, however, this time from their MAC is 2ns to 3ns. Is there any solution?

Thank you!

John