Tool/software:

Hello guys,

One of my customers is considering using DP83822H for their new products.

At this moment, they have the following question.

Could you please give me your reply?

Q.

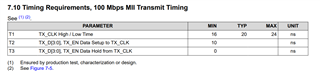

They are considering using this device with MII, 100BASE-TX.

and they want to know setup/hold time between XI(master clock input) and TX_D[1:0],TX_EN signal.

They found the following timing regulations for RMII case.

TX_D[1:0] and TX_EN Data Setup to XI rising

TX_D[1:0] and TX_EN Data Hold from XI rising

But they didn't find these regulation for MII case.

Could you please tell me these setup/hold timing regulation value?

Your reply would be much appreciated.

Best regards,

Kazuya.