Other Parts Discussed in Thread: AFE7951,

Tool/software:

I am using AFE7950EVM and AFE7951 ICs

I need information on the JESD input/output configuration of the AFE7950EVM board.

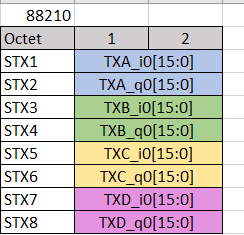

1. I want to know how the 8 inputs are mapped to each of the 4 DACs.

2. I want to know how the JESD data is configured for each input, which is a 14-bit DAC input.

For example, JESD is basically 8-bit, but to input 14-bit, do I need to input 8-bits twice (discarding the upper 2 bits) or do I need to input 8-bits to an input (say SRX1) and input 8-bits to another input (say SRX2) (discarding the upper 1 bit)?