Tool/software:

Hi,

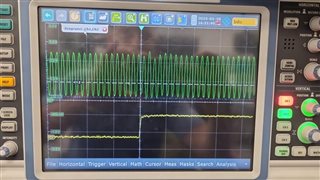

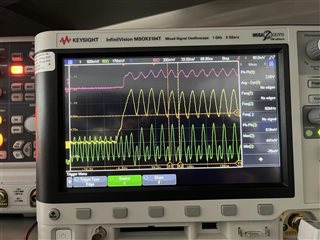

we have connected the EVM to receive only and we are sampling the data on the RXD/CLK/ER/DV signals (2Gserdes, 100Mhz parallel - GTX_CLK).

the device is syncing (RX_DV/ER deassert) and we are sampling the parallel data using an FPGA board (MPSOC based).

we observe sampling mismatches of whole 16bit words in specific places, after 'hffff data is transmitted for example.

all the reset of the data seems correct. no loose of sync detected and no deassertion of ER detected.

please assist in finding what might be the cause ?

we suspect weak RX_CLK once higher current is pulled by the board. we observe it is changing "shape" once we receive those culprits words.

Thanks

Doron