Part Number: DS250DF230

Tool/software:

Hello,

in our application we use two DS250DF230 to send data over an ambitious channel from 5Gbit/s to 6,25Gbit/s. For an extension it should be perfect to use the recovered clock output as syncronized reference for additional equipment on both sides.

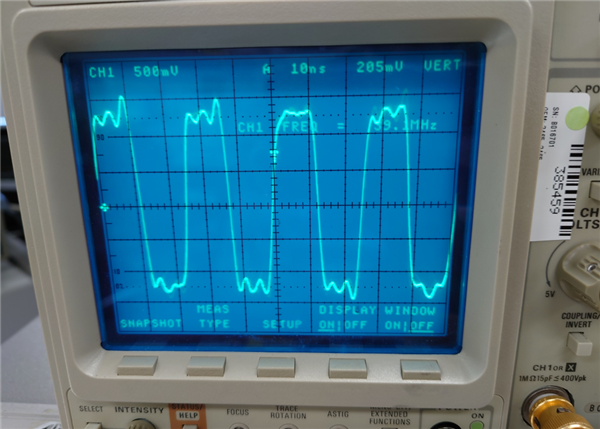

We followed the instructions in the programming manual and in fact, the output is putting out some signal. But instead of the expected rectangular clock-signal in the 30Mhz-Range, there some instable sinus in 10khz-range or even slower rising and falling edges. With unlocked CDR or switching off the output there is no signal, so we assume the basic configuration is right.

As we run actually with manual clock-rate-configuration, we tried setting the rclk-divider(rclk_sel_div_lv, mr_cipri_clk_div_sel_ov set to one) to different values. Output changes somehow, but we still have something like mentioned above.

For the desired purpose we aren't limited to the bitrates we used before, so we tried some standard-bitrate-configurations as well(set in 0x2F), unfortunately without success.

Does anybody have more experience with this output and can give us some hint(s) how to get this running?

Many thanks in advance,

Philipp