Part Number: DS90UB954-Q1

Tool/software:

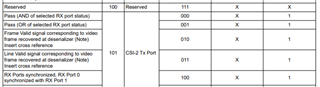

CSI-2 Tx Port PASS is not asserted either in CSI_STS 0x35 [0] or or when routed to GPIO with GPIOx Output Function set to 0x15 (AND) or 0x35 (OR)

However, both RX Port 0 Lock indication and RX Port 0 Pass indication are asserted when routed to the same GPIO. Additionally, both RX Port 0 Frame Valid signal and RX Port 0 Line Valid signal are present and look correct (also LINE_COUNT and LINE_LEN in registers 0x73 to 0x76 are also correct).

Video frame is 1500 active lines by 1875 bytes (1500 10-bit pixels) at 60 Hz with sensor having 2 MIPI outputs at 780 Mbps each. Only RX0 is used. Serializer is reporting correct sensor MIPI statistics.

DEVICE_STS 0x04 = 0xDF, RX_PORT_STS1 0x4D = 0x03

RX_PORT_STS2 0x4E = 0x14 (buffer error due to CSI-2 TX not functioning?)

CSI_STS 0x35 = 0x00

RX_FREQ_HIGH 0x4F = 0x64 RX_FREQ_LOW 0x50 = 0x00

CSI_RX_STS 0x7A = 0x00

I have configured the following registers:

General Configuration 0x02 = 0x3E

RX_PORT_CTL 0x0C = 0x81

CSI_PLL_CTL 0x1F = 0x02 (setting to 0x00 has no effect on buffer errors)

FWD_CTL1 0x20 = 0x20, FWD_CTL2 0x21 = 0xC0

CSI_CTL 0x33 = 0x23, CSI_CTL2 0x34 = 0x40

Any suggestions?

Thanks!