Part Number: SN65DSI86EVM

Other Parts Discussed in Thread: SN65DSI86

Tool/software:

I use SN65DSI86EVM connect to our EVB (SSD2828 mipi bridge), the panel module can not be display.

The SN65DSI86 initial code and AUX & Mainlink waveform is list as below:

//------------------------------------------------------------------------------------------------------------

SN65DSI_REG_WR(0x0A,0x06); // REFCLK 27Mhz

Sleep(1);

SN65DSI_REG_WR(0x10,0x26); // Dual port / 4 DSI lanes/ CHA for LEFT image , CHB for RIGHT image

Sleep(1);

SN65DSI_REG_WR(0x12,0x59); // DSIA clk freq 750Mhz

Sleep(1);

//SN65DSI_REG_WR(0x13,0x96); // DSIB clk freq 450Mhz

//Sleep(1);

SN65DSI_REG_WR(0x5A,0x05); // enhanced framing

Sleep(1);

SN65DSI_REG_WR(0x93,0x20); // Pre0dB 2 lanes no SSC

//SN65DSI_REG_WR(0x93,0x30); // Pre0dB 4 lanes no SSC

Sleep(1);

SN65DSI_REG_WR(0x94,0x80); // L3mV HBR2(5.4Gbps/per lane)

Sleep(1);

SN65DSI_REG_WR(0x0D,0x01); // PLL enable

Sleep(1);

SN65DSI_REG_WR(0x95,0xC0); // POST2 0dB

Sleep(1);

//-------------------------------------------------

SN65DSI_REG_WR(0x64,0x01); // Enable ASSR write DPCD register 0x0010A with 0x01 (DPCD data)

SN65DSI_REG_WR(0x74,0x00); // Enable ASSR write DPCD register 0x0010A with 0x01 (DPCD address mmsb)

SN65DSI_REG_WR(0x75,0x01); // Enable ASSR write DPCD register 0x0010A with 0x01 (DPCD address msb)

SN65DSI_REG_WR(0x76,0x0A); // Enable ASSR write DPCD register 0x0010A with 0x01 (DPCD address lsb)

SN65DSI_REG_WR(0x77,0x01); // Enable ASSR write DPCD register 0x0010A with 0x01 (AUX length)

SN65DSI_REG_WR(0x78,0x81); // Enable ASSR write DPCD register 0x0010A with 0x01 (AUX command , start)

SN65DSI_REG_WR(0x96,0x04); // semi-Auto TRAIN

SN65DSI_REG_WR(0x20,0x80); // H_res_lsb for mipi chA 1920

SN65DSI_REG_WR(0x21,0x07); // H_res_msb for mipi chA

SN65DSI_REG_WR(0x24,0x38); // V_res_lsb for mipi chA/chB 1080

SN65DSI_REG_WR(0x25,0x04); // V_res_msb for mipi chA/chB

SN65DSI_REG_WR(0x2C,0x2C); // Hsync_width_lsb for mipi chA/chB

SN65DSI_REG_WR(0x2D,0x00); // Hsync_width_msb for mipi chA/chB

SN65DSI_REG_WR(0x34,0x94); // HBP for mipi chA/chB

SN65DSI_REG_WR(0x38,0x58); // HFP for mipi chA/chB

SN65DSI_REG_WR(0x30,0x05); // Vsync_width_lsb for mipi chA/chB

SN65DSI_REG_WR(0x31,0x80); // Vsync_width_msb for mipi chA/chB

SN65DSI_REG_WR(0x36,0x24); // VBP for mipi chA/chB

SN65DSI_REG_WR(0x3A,0x04); // VFP for mipi chA/chB

SN65DSI_REG_WR(0x5B,0x00); // DP-24BPP enaable

SN65DSI_REG_WR(0x3C,0x00); // color bar disabled

SN65DSI_REG_WR(0x5A,0x0D); // enhance framing and Vstream enable

//---------------------------------------------------------

//------------------------------------------------------------------------------------------------------------

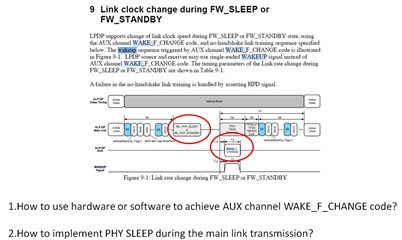

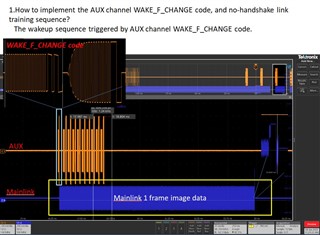

How to implement the AUX channel WAKE_F_CHANGE code, and no-handshake link training sequence?

The wakeup sequence triggered by AUX channel WAKE_F_CHANGE code.

Thank very much.

Best Regards

Jackson Huang