Part Number: DP83TC812S-Q1

Tool/software:

Hello team,

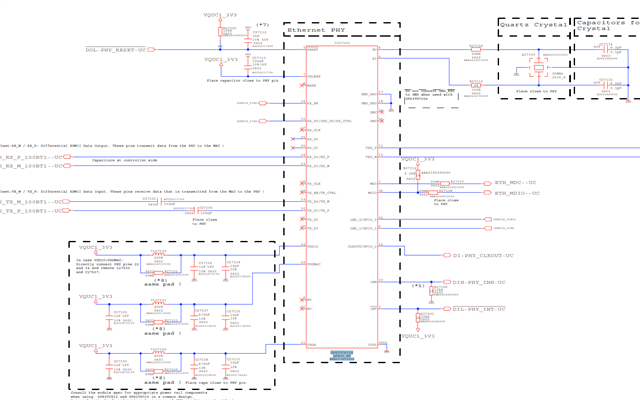

My customer is working on the PHY bring-up of DP83TC812S PHY chip.

The intended configuration for PHY is as below,

Mode – Master

Speed – 100 Mbit

MII mode – SGMII

The bootstrap pin configuration is as below.

Currently, it is observed that PHY is not in Link up state.

The link partner is configured as Master/Slave auto configuration at 100 Mb.

Register dump as per troubleshooting guide.

DP83TC812S BootStrap Config.xlsxDP83TC812S_RegDump.xlsx

Please take a look and let us know the root cause for this issue.

Thanks

Regards,

Daniel Wang