Other Parts Discussed in Thread: TDP0604, TDP1204, TMDS1204, TDP158

Tool/software:

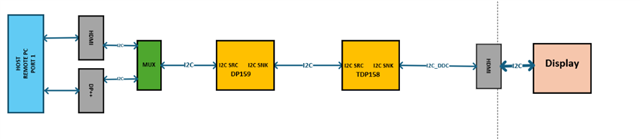

Hi

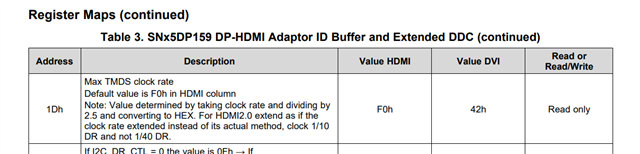

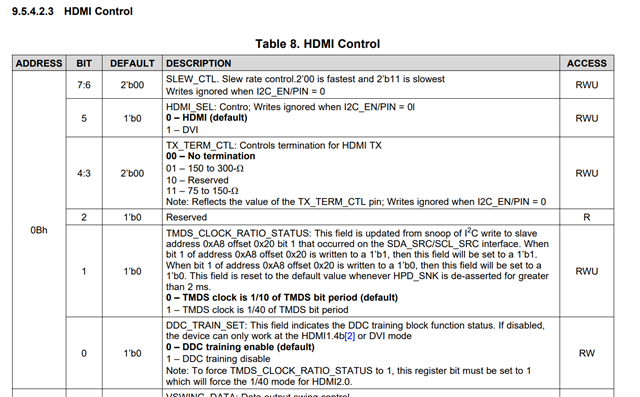

I am connecting from the DP++ connector directly to the component without 100NF series capacitors, could this affect the fact that I am unable to work with 4K screens, only with HDMI,

and if I connect via an HDMI connector that is connected to the component via series capacitors, in this case I am able to work with 4K screens

or is something else affecting it?