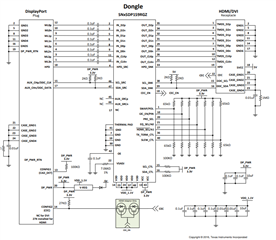

Part Number: TDP0604

Other Parts Discussed in Thread: SN65DP159, DP159RGZEVM,

Tool/software:

Hello TI

Our application uses an Intel processor on a COMe computer board.

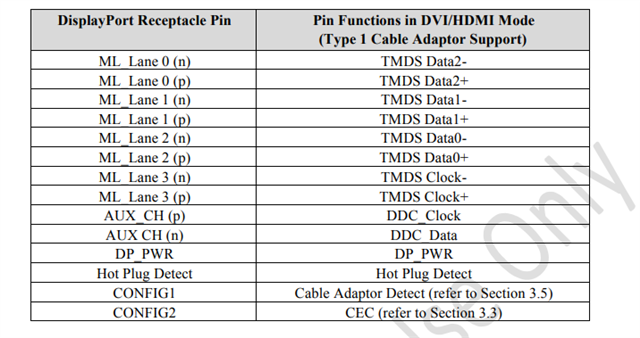

We are using the DDI for monitor output. The datasheet for the computer module specifies DDI is DP++ capable.

We want to output video to an external DVI monitor.

However, the external monitor does not support the DDC interface, but has fixed known resolution.

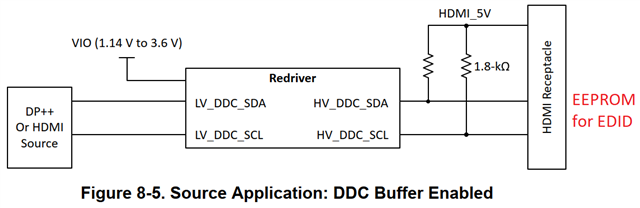

Can the TDP0604 or SN65DP159 be used in this case? Is the DDC interface required?

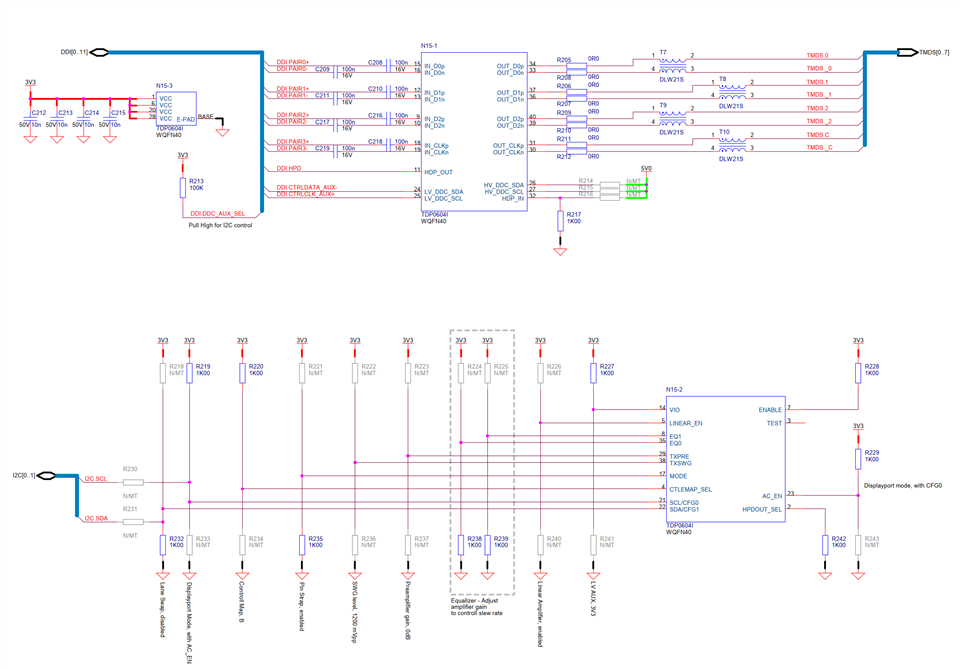

Also, how should we couple the in- and outputs with respect to AC and DC?

We currently have an implementation using the TDP0604 with AC coupled inputs and DC coupled outputs, this setup is currently not working.

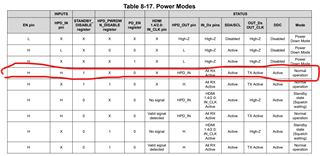

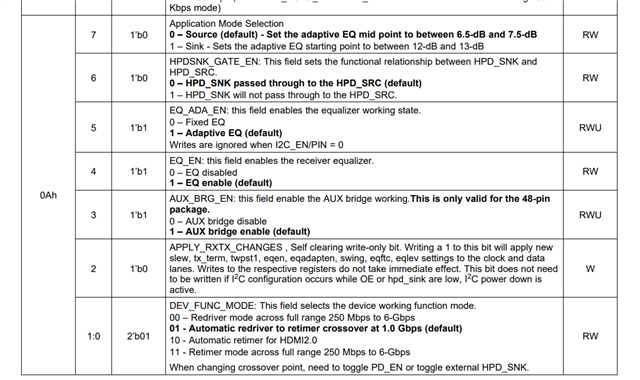

We intend to use the TDP0604 in strap mode.

We have attempted to add a pull up resistor to 5V on HPD_IN with no success.

Can you please help us get closer to a solution?

Regards

Lars