Tool/software:

hi team,

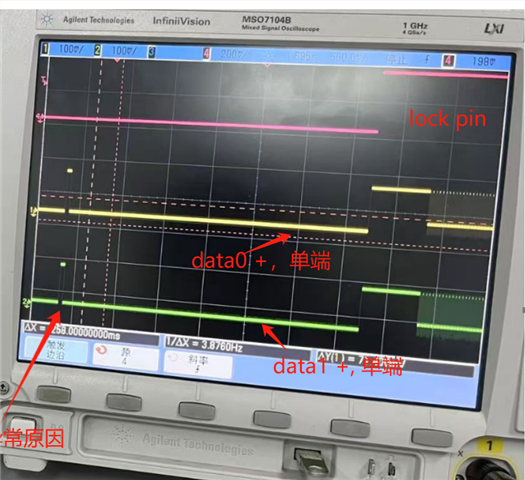

may you check the status of CSI-output behavior of 940 during lock=L? Customer find data lane (CSI0 D0+/D1+ stays high for ~50mS/120mV) while lock stays low which trigger the SOC enters fault state.

Is this expect behavior? CSI status is undefined if lock is L (940 finished initialization with CSI configured).

If so, how to configure CSI to defined status once LOCK drops?