Tool/software:

Hi,

We are currently using the UCC24624 in an LLC resonant converter and are facing a problem where the SR MOSFET gate turns OFF before the drain current reaches zero. This results in extended body diode conduction, leading to increased power loss and heating.

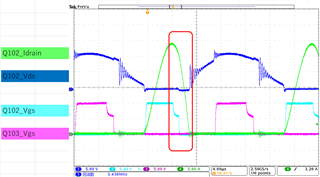

As shown in the attached waveform (highlighted in red), significant drain current remains at the time of gate turn-off.

Based on the datasheet, we suspect this is due to the fixed VTHVGOFF = 10.5 mV turn-off threshold.

We have already implemented the recommended resistor between the VSS pin and the MOSFET source to increase the turn-off threshold, but did not observe significant improvement.

We would appreciate your guidance on the following points:

-

Is such early turn-off behavior commonly attributed to parasitic inductance or MOSFET package-related effects?

-

Are there any additional countermeasures beyond adjusting the VSS threshold that may be more effective?

-

Do you have any recommendations regarding PCB layout (e.g., routing of VD/VSS or PGND) to help mitigate this issue?

Thank you very much for your support.

Conor