Part Number: DP83867E

Tool/software:

Dear all,

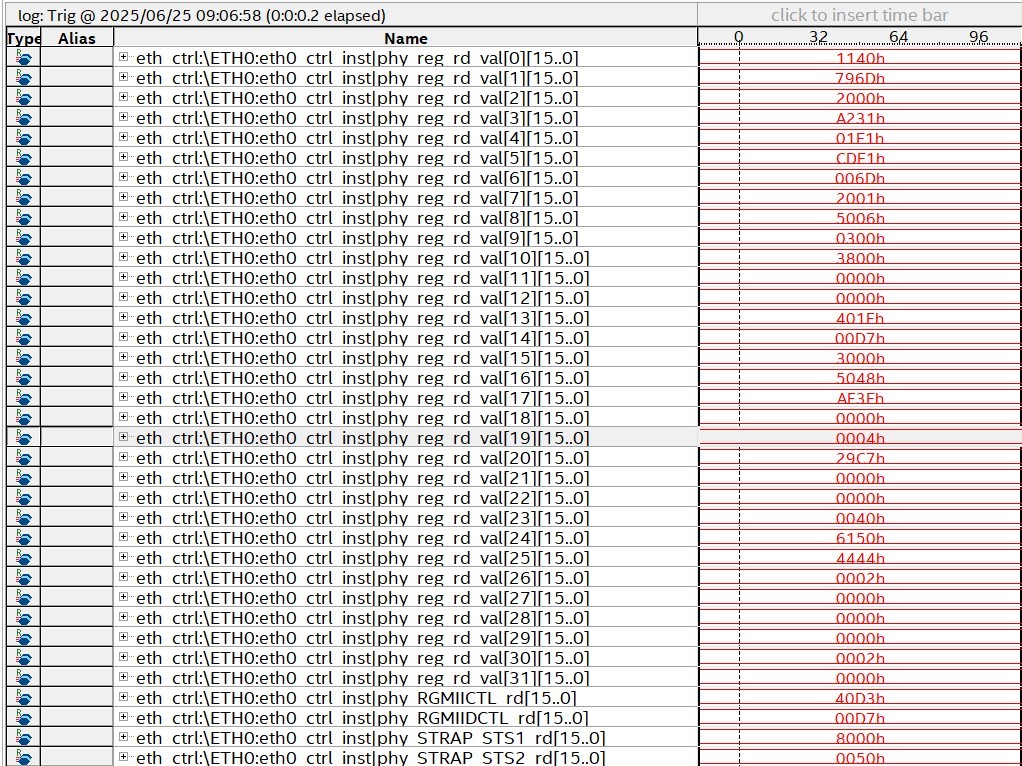

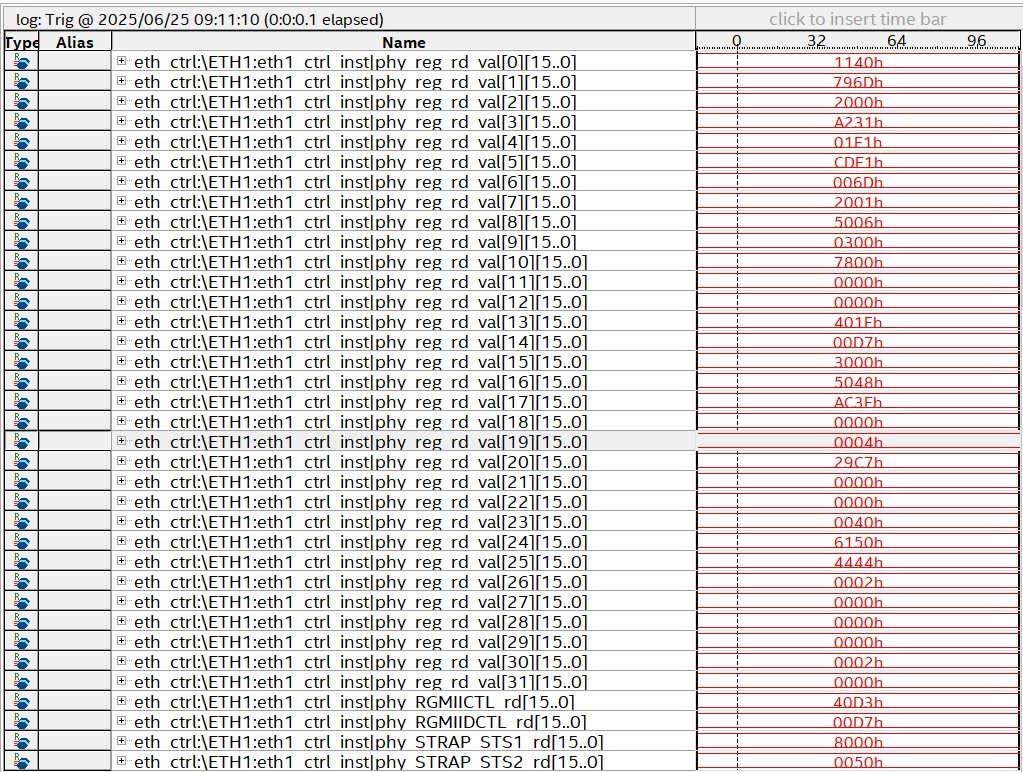

We are currently debugging a Cyclon V FPGA (commercial Ethernet IP block) design with two Dp83867E Ethernet Transceiver.

The issue is an xGMII Error interrupt, which prevents testing with the IC's internal loopback functions between the PHU and the FPGA itself.

At 10MBits we get data transmitted out to the physical layer, but not at higher speeds.

Clocks are stable and precise, within specs. Checked at XI and XO.

FPGA - dp83867e RX/TX trace lengths are well within delay specs, less than 0.256mm length difference.

After a reset of the xGMII error it reappears instantly.

Any good suggestions on how to interpret the xRGMII error interrupt?