Part Number: DP83848C

Tool/software:

Hi,

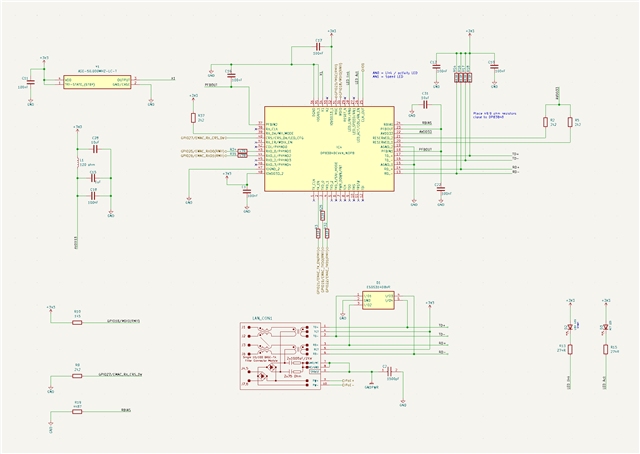

I’m working on a prototype which uses the DP83848C to interface to an ESP32 using RMII. At present I’m unable to configure the PHY start up with auto-negotiation enabled.

I use pins 26 and 28 to drive LEDs directly. Each LED is connected to 3V3 via a 274-ohm resistor. Pin 27 is not connected and relies on the internal pull-up resistor for the strapping value.

When the DP83848C starts up, it looks like the preferred forced mode value is 100 Half-Duplex.

By changing our network switch setting we can obtain an IP address and send / receive data at the following forced mode values.

10 Half-Duplex

10 Full-Duplex

100 Half-Duplex

100 Full-Duplex

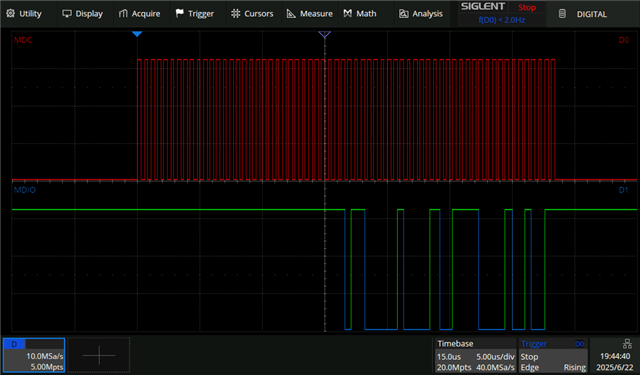

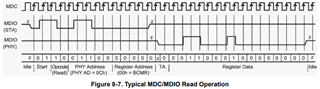

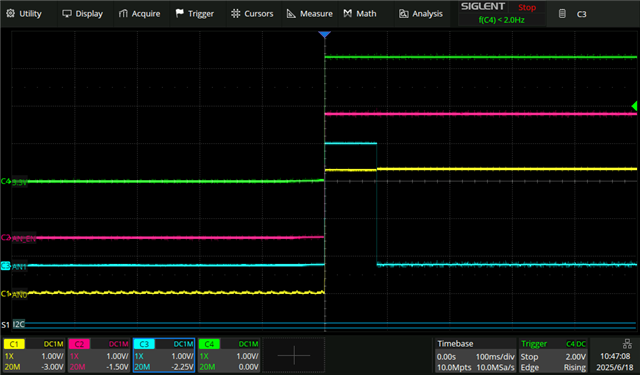

From the trace there seems to be an issue with the strapping value of AN1 pin 27. This does not align with the information provided in the datasheet.

This particular trace shows the normal start-up of the device but even if I connect an external pull-up resistor (2k2 ohm) to pin 27, the trace remains the same.

The other issue I’ve noticed is that PHY Identifier Registers #1 and #2 report incorrect values. Address 0x02h reports 0x4001 while address 0x03h reports 0xB921. Giving a non-standard OUI: 0x10006E, Non-standard model: 0x12 and Model Revision: 0x1.

Any help is gratefully received.