Part Number: DP83867E

Tool/software:

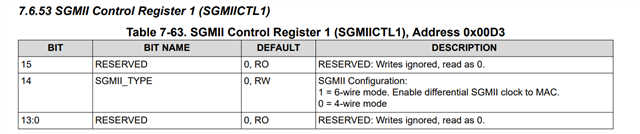

The DP83867E SGMII EVM evaluation-board has an SGMII-interface consisting of one transmit differential lane, one receive differential lane and one clock differential lane. I would like to remove the differential lanes for the clock so that the SGMII-Interface will embed the clock in the data-streams. How could I achieve this configuration? Please let me know which all registers of DP83867E have to be modified and what are the modifications,

Regards,

Jaidev