Other Parts Discussed in Thread: DP83TD510E-EVM, , DP83TD510E

Tool/software:

Hi,

I have a design that uses the DP83822I and DP83TD510E in a back to back media converter application. Both receive clock lines from a single 50Mhz cmos oscillator. I have followed the bootstrap resistors setup given in the schematic of the DP83TD510E-EVM exactly for the DP83822I. The MDIO/MDC lines of both ICs are tied together with the MDIO line having a 2.2KOhm pull-up resistor to 3.3V.

It seems no matter what I do, when I power my application and check the ethernet configuration using ethtool, the result is the ethernet always auto-negotiating as half-duplex when I'd prefer full-duplex. I have even tried force bootstrapping the IC into 10BASE-Te full-duplex and the result is the same. This is not what I see when using the DP83TD510E-EVM kit. The DP83TD510E-EVM kit does correctly negotiate as full-duplex.

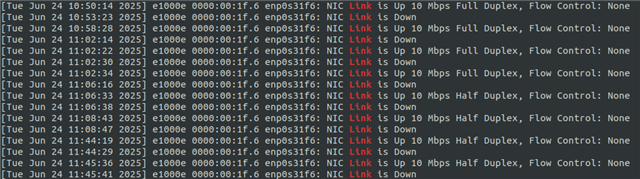

See below dmesg log:

All full-duplex entries are the DP83TD510E-EVM kit and all half-duplex entries are my application. I'm not sure where I am going wrong. Please can someone kindly assist. Thank you in advance.