Part Number: DS160PR410

Tool/software:

Dear,

We're currently facing a critical issue involving the DS160PR410RNQR.

Below are the detailed observations and background.

Issue Summary

- Failure Rage : Approximately 20~40% during initial setup and operation

- Behavior :

>The device operates normally at first but fails after a certain period of runtime.

> I2C communication is stable and accessible even during the failure.

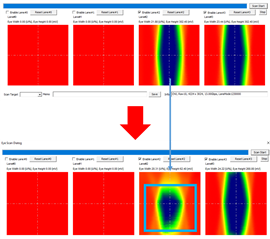

>One of the image lanes stops functioning (e.g., Lane2) randomly (refer to attached image1)

>The failed lane only recovers when the IC is physically replaced.

>Reattaching the previously failed IC reproduces the same failure.

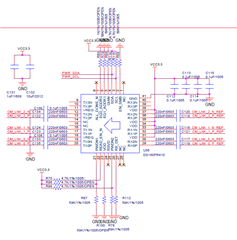

-The circuit was designed based on the reference schematic in TI's datasheet. (refer to attached image2)