Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Tool/software:

HI Team,

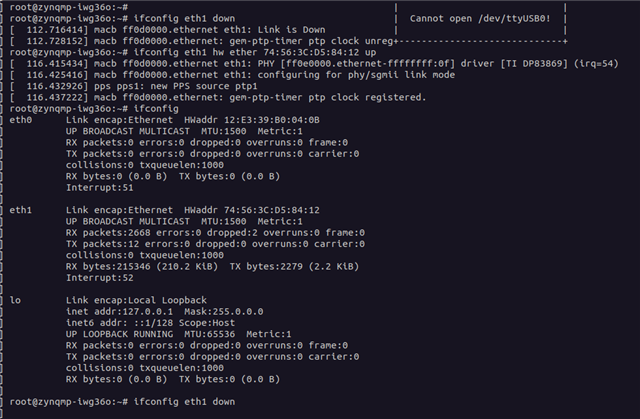

I am currently working on a custom board based on the Xilinx Zynq UltraScale+ MPSoC and using the Texas Instruments DP83869HMRGZT Ethernet PHY. We are encountering a critical issue where the PHY is not consistently detected during the boot process.

In some instances, the PHY is correctly detected by U-Boot, while in others, it fails to initialize. This intermittent behavior is impacting the reliability of our system and is a major concern for our project.

Could you please assist us in identifying the root cause and suggest possible solutions or debugging steps to ensure consistent PHY detection?

below are my dts settings

&gem1 {

phy-mode = "rgmii";

status = "okay";

phy-handle = <&phy1>;

phy1: phy@1 {

reg = <1>;

compatible = "ethernet-phy-ieee802.3-c22";

tx-fifo-depth = <0x01>;

rx-fifo-depth = <0x01>;

ti,op-mode = <0x00>;

rx-internal-delay-ps = <3000>;

tx-internal-delay-ps = <2000>;

interrupt-parent = <&gpio>;

interrupts = <78 8>;

};

};

Regards,

Madhusankar