Part Number: DP83869HM

Tool/software:

Greetings for the day,

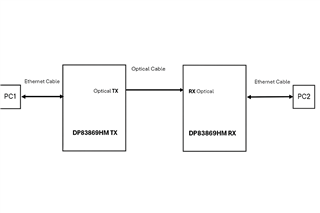

I have raised a query(link is mentioned below) few months back related to Optical RX Spoofing and I got clarification for my query. In the query we have suggsted to Set Bit 15 of register D4 to enable Optical RX Spoofing, which was successful. But that solution is creating another problem i.e. internal loopback. We are getting back copy of data which we have sent. Which should not happen.

So my question is how to disable internal loopback and enable only RX Spoofing?

And one more thing is there any way to disable TX line of Opticl port.

Thank You.

Regards,

Balaji TS