Part Number: TCAN4550

Tool/software:

Hi,

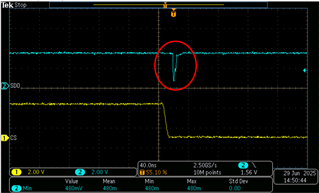

On TCAN4550 we have the following negative spike on SDO while enabling the nCS as shown below.

According to spec this pin is high impedance until the SPI output is enabled via nCS.

Is there some register setting which prevent this negative spike?

Thanks,

Zion.